Specificazione

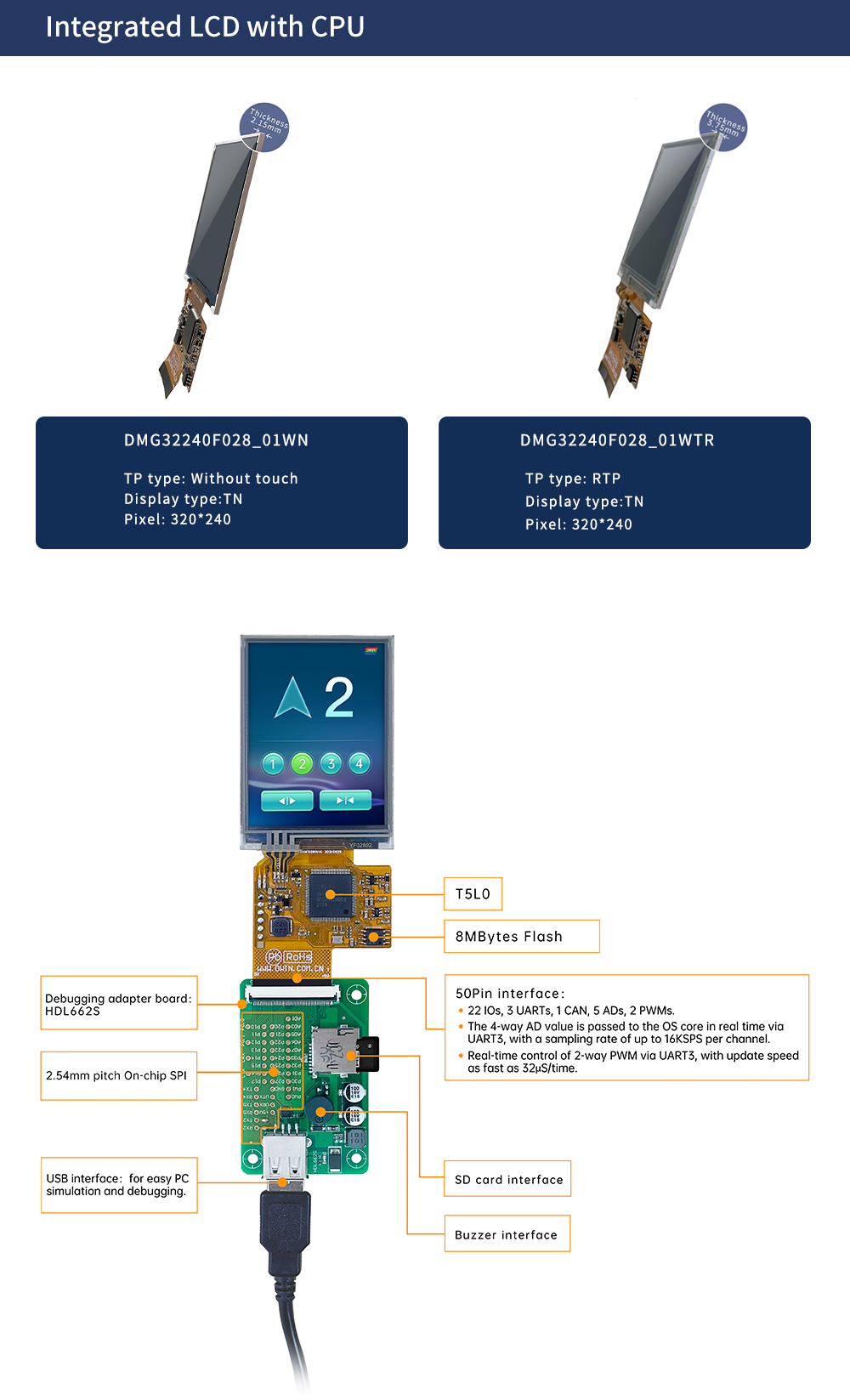

| T5L0 ASIC | L'ASIC T5L0 hè un ASIC dual-core à chip unicu, di bassa putenza, costu-efficace, è applicazione altamente integrata cuncepitu da DWIN Technology per LCD di piccula dimensione è prodotta in massa in 2020. | ||

| Culore | 262K culori | ||

| Tipu LCD | TN, TFT LCD | ||

| Angulu di vista | Angolo di visione normale, valore tipico di 70°/70°/50°/70° (L/R/U/D) | ||

| Zona di visualizazione (AA) | 43,2 mm (L) × 57,6 mm (H) | ||

| Risoluzione | 240 * 320 | ||

| Retroilluminazione | LED | ||

| Luminosità | DMG32240F028_01WN: 350 nit DMG32240F028_01WTR: 300 nit | ||

| Tipu | RTP (Panel Touch Resistivu) | ||

| Struttura | Film ITO + vetru ITO | ||

| Modu Touch | Puntu di sustegnu toccu è trascina | ||

| Durezza di a superficia | 3H | ||

| Trasmissione di luce | Più di 80% | ||

| A vita | Dotting> 1.000.000 volte;Stroke> 100.000 volte;150 g di forza, avanti è avanti cuntatu cum'è duie volte | ||

| Tensione di putenza | 3.6 ~ 5.5V, valore tipicu di 5V | ||

| Operazione attuale | 110 mA VCC = 5 V, retroilluminazione max | ||

| WTC:- WN: 75mA VCC = 5V, retroilluminazione spenta | |||

| Temperature di travagliu | -10 ℃ ~ 60 ℃ | ||

| Temperature di almacenamiento | -20 ℃ ~ 70 ℃ | ||

| Umidità di travagliu | 10% ~ 90% RH, valore tipicu di 60% RH | ||

| Interfaccia d'utilizatore | 50Pin_0.5mm FPC | ||

| Baudrate | 3150 ~ 3225600 bps | ||

| Tensione di Output | Output 1; 3,0 ~ 3,3 V | ||

| Output 0;0~0,3 V | |||

| Tensione di input (RXD) | Ingressu 1;3.3V | ||

| Ingressu 0; 0 ~ 0,5 V | |||

| Interfaccia | UART2: TTL; UART4: TTL; (Solu dispunibule dopu a cunfigurazione OS UART5: TTL; (Solu dispunibule dopu a cunfigurazione OS) | ||

| Format di dati | UART2: N81; UART4: N81/E81/O81/N82; 4 modi (configurazione OS) UART5: N81/E81/O81/N82; 4 modi (configurazione OS) | ||

| Pin | Definizione | I/O | Descrizzione Funziunale |

| 1 | 5V | I | Alimentazione, DC3.6-5.5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ADC di input.Risoluzione 12-bit in casu di alimentazione 3.3V.Tensione di entrata 0-3.3V.Eccettu per AD6, i dati di u restu sò mandati à u core OS via UART3 in tempu reale cù una freccia di campionamentu di 16KHz.AD1 è AD5 pò esse usatu in parallelu, è AD3 è AD7 pò esse usatu in parallelu, chì uguali à dui 32KHz sample AD.AD1, AD3, AD5, AD7 pò ièssiri usatu in parallelu, chì uguali à un 64KHz sample AD;i dati sò sommati 1024 volte è dopu divisu da 64 per ottene un valore AD 64Hz 16bit per oversampling. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD2 | I | |

| 11 | 3.3 | O | Uscita 3.3V, carica massima di 150mA. |

| 12 | SPK | O | MOSFET esternu per guidà buzzer o parlante.A resistenza esterna di 10K deve esse tirata à a terra per assicurà chì a putenza hè bassa. |

| 13 | SD_CD | I/O | Interfaccia SD/SDHC, L'SD_CK cunnette un condensatore 22pF à GND vicinu à l'interfaccia di a carta SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | I/O | |

| 16 | SD_D2 | I/O | |

| 17 | SD_D1 | I/O | |

| 18 | SD_D0 | I/O | |

| 19 | PWM0 | O | 2 uscita PWM a 16 bit.A resistenza esterna di 10K deve esse tirata à a terra per assicurà chì a putenza hè bassa. U core OS pò esse cuntrullatu in tempu reale via UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | I/O | Se utilizate RX8130 o SD2058 I2C RTC per cunnette à i dui IO, SCL deve esse cunnessu à P3.2, è SDA cunnessu à P3.3 in parallelu cù resistenza di 10K pull-up à 3.3V. |

| 22 | P3.2 | I/O | |

| 23 | P3.1/EX1 | I/O | Pò esse usatu cum'è una interruzzione esterna 1 input à u stessu tempu, è supporta tramindui i modi d'interruzzione di u livellu di bassa tensione o di u trailing edge. |

| 24 | P3.0/EX0 | I/O | Pò esse usatu cum'è un input di interruzzione esterna 0 à u stessu tempu, è supporta tramindui modi d'interruzzione di u livellu di bassa tensione o di u trailing edge. |

| 25 | P2.7 | I/O | interfaccia IO |

| 26 | P2.6 | I/O | interfaccia IO |

| 27 | P2.5 | I/O | interfaccia IO |

| 28 | P2.4 | I/O | interfaccia IO |

| 29 | P2.3 | I/O | interfaccia IO |

| 30 | P2.2 | I/O | interfaccia IO |

| 31 | P2.1 | I/O | interfaccia IO |

| 32 | P2.0 | I/O | interfaccia IO |

| 33 | P1.7 | I/O | interfaccia IO |

| 34 | P1.6 | I/O | interfaccia IO |

| 35 | P1.5 | I/O | interfaccia IO |

| 36 | P1.4 | I/O | interfaccia IO |

| 37 | P1.3 | I/O | interfaccia IO |

| 38 | P1.2 | I/O | interfaccia IO |

| 39 | P1.1 | I/O | interfaccia IO |

| 40 | P1.0 | I/O | interfaccia IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | I/O | interfaccia IO |

| 46 | P0.1 | I/O | interfaccia IO |

| 47 | CAN_TX | O | interfaccia CAN |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (portu seriale UART0 di u core OS) |

| 50 | UART2_RXD | I |

Modèle : TC040C12 U(W) 00

Modello: DMG48320F035_01W (Serie COF)