Promozione di vendita calda di a pantalla intelligente T5L di DWIN

L'LCM intelligenti COF di a serie F seranu prudutte in massa prestu

schermu COF 4.0-inch

schermu COF 5.0-inch

schermu COF 7.0-inch

I primi mudelli in massa

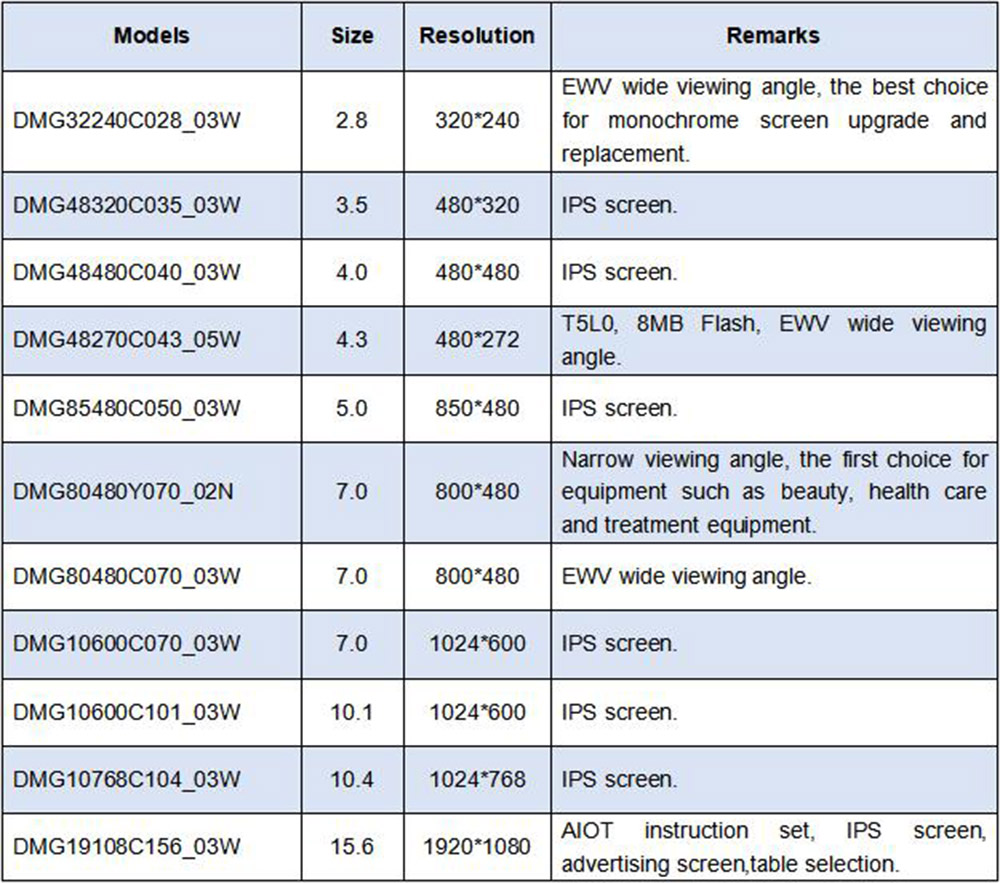

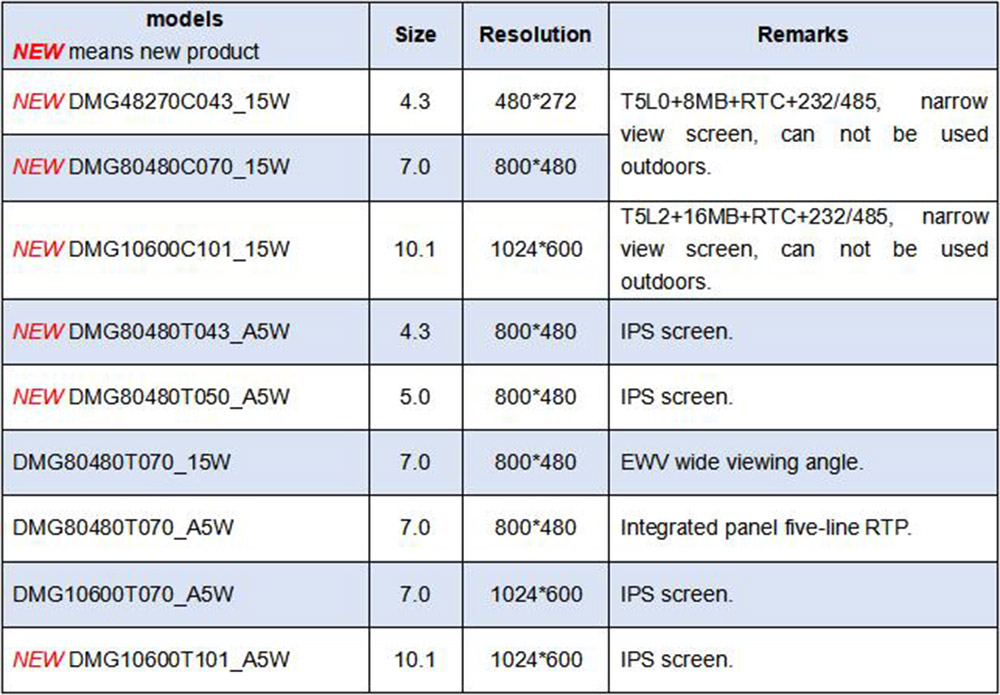

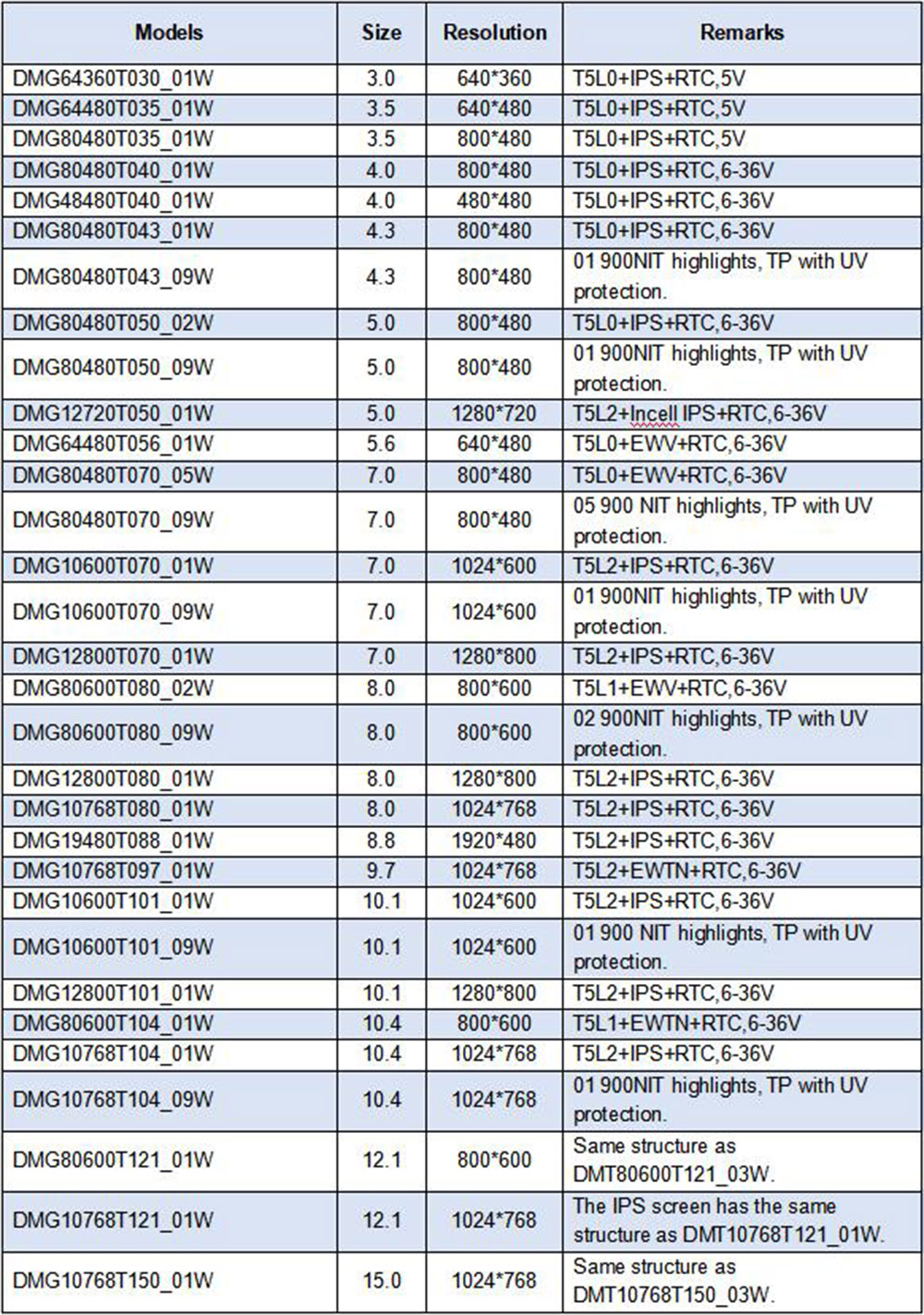

| Mudellu | Size Screen (inch) | Risoluzione (pixel) | Prezzu di riferenza (13% VAT inclusa) | Rimarche | ||

| WN | WTR | WTC | ||||

| DMG32240F028_01W | 2.8 | 320 * 240 | 45 | 50 | \ | Angulu di vista largu |

| DMG48320F035_01W | 3.5 | 480 * 320 | 70 | \ | 95 | IPS.Aspectu alternativu per biancu o neru integratu.TP neru integratu cumplettamente laminatu per u screnu WTC. |

| DMG48480F040_01W | 4.0 | 480 * 480 | 68 | \ | 98 | IPS.Aspectu alternativu per biancu o neru integratu.TP neru integratu cumplettamente laminatu per u screnu WTC. |

| DMG48270F043_01W | 4.3 | 480 * 272 | 59 | 65 | \ | Angulu di vista nurmale |

| DMG80480F043_01W | 4.3 | 480 * 800 | 68 | \ | 95 | IPS.Aspectu alternativu per biancu o neru integratu.TP neru integratu cumplettamente laminatu per u screnu WTC. |

| DMG85480F050_01W | 5.0 | 480 * 854 | 76 | \ | 110 | IPS.Aspectu alternativu per biancu o neru integratu.TP neru integratu cumplettamente laminatu per u screnu WTC. |

| DMG80480F070_01W | 7.0 | 800 * 480 | 95 | 105 | \ | Angulu di vista nurmale |

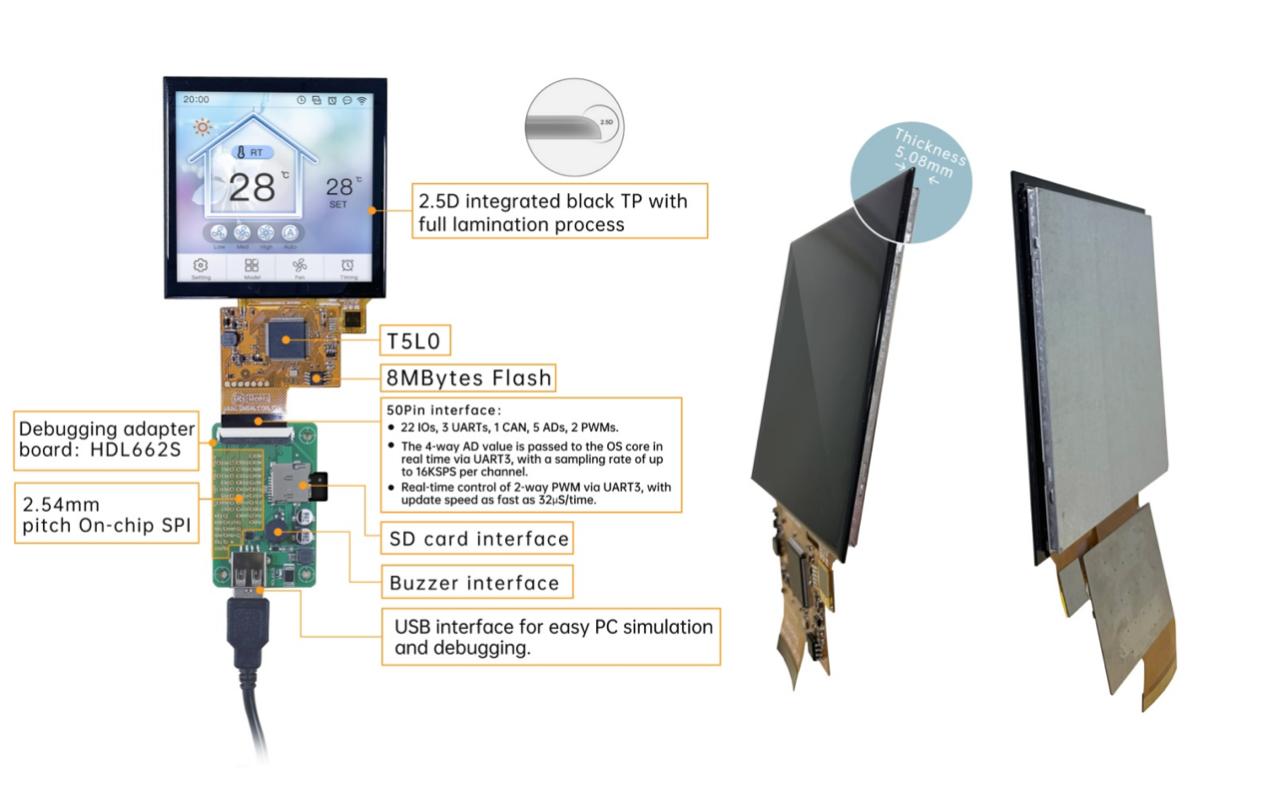

I schermi di a serie F usanu una interfaccia FPC unificata 50Pin 0.5mm pitch à u latu di l'utilizatori.

A definizione di l'interfaccia hè a siguenti.

| Pin | Definizione | I/O | Descrizzione |

| 1 | + 5V | I | Input di alimentazione, DC3.6-5.5V. |

| 2 | + 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ADC di input.Risoluzione 12-bit.Tensione di entrata 0-3.3V. A rata di campionamentu di dati di un canale unicu hè 16KHz è e dati di AD1, AD3, AD5 è AD7 sò passati à u core OS in tempu reale via UART3.4 canali ponu esse utilizati in parallelu per aumentà a rata di campionamentu à 64KSPS.I valori AD 64SPS 16bit ponu esse ottenuti per oversampling. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | + 3,3 | O | Uscita 3.3V, carica massima di 150mA. |

| 12 | SPK | O | Buzzer esterno o parlante. |

| 13 | SD_CD | IO | Interfaccia SD/SDHC. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | 2 uscita PWM a 16 bit. U core OS pò esse cuntrullatu in tempu reale via UART3 cù un tempu minimu di aghjurnamentu di 32μs. |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | Pò esse usatu cum'è una interruzzione esterna 1 input à u stessu tempu, è supporta tramindui i modi d'interruzzione di u livellu di bassa tensione o di u trailing edge. |

| 24 | P3.0/EX0 | IO | Pò esse aduprata cum'è una interruzzione esterna 0 input à u stessu tempu, è supporta tramindui i modi d'interruzzione di u nivellu di bassa tensione o di u trailing edge. |

| 25 | P2.7 | IO | |

| 26 | P2.6 | IO | |

| 27 | P2.5 | IO | |

| 28 | P2.4 | IO | |

| 29 | P2.3 | IO | |

| 30 | P2.2 | IO | |

| 31 | P2.1 | IO | |

| 32 | P2.0 | IO | |

| 33 | P1.7 | IO | |

| 34 | P1.6 | IO | |

| 35 | P1.5 | IO | |

| 36 | P1.4 | IO | |

| 37 | P1.3 | IO | |

| 38 | P1.2 | IO | |

| 39 | P1.1 | IO | |

| 40 | P1.0 | IO | |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | |

| 46 | P0.1 | IO | |

| 47 | CAN_TX | O | CAN |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 |

| 50 | UART2_RXD | I |

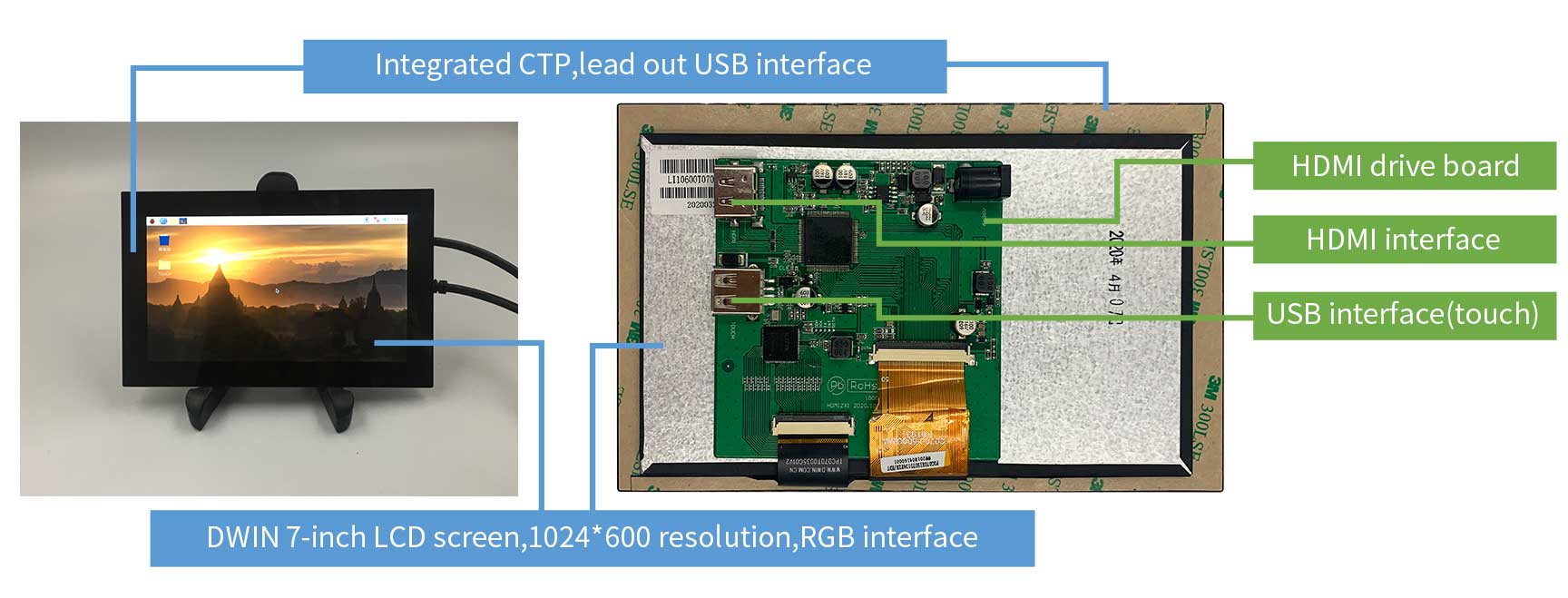

A Soluzione di Display di Interfaccia HDMI di Alta Qualità DWIN hè liberata

Vantaghji di a suluzione DWIN

Tempu di post: 12-novembre-2021